- JTAG(Joint Test Action Group),利用邊界掃描的方式,依序的做Shift and Capture for each test Vector,即可對HardWare內部的Flip-Flop做Debug的動作.

優點: 簡單,不需要用到Probe的方式,可針對內部的Scan-Flip-Flop.

缺點: Boundary Scan Length/Scan Length過大時,會降低Debug的效能.

Pin Assignment

TDI (Test Data In)

TDO (Test Data Out)

TCK (Test Clock)

TMS (Test Mode Select)

TRST (Test Reset) optional

利用TDI/TDO的 I/O端口做Vector的輸入跟輸出, Test Vector in(TDI), Result out(TDO),

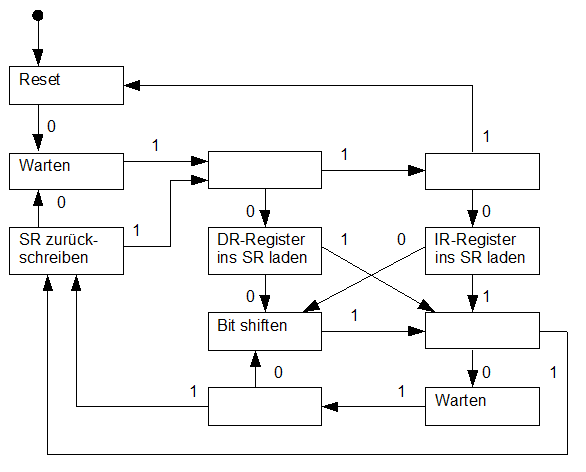

TMS為FSM Mode Select, TCK為Trigger Clock, TRST 為系統Reset.

Ref: http://en.wikipedia.org/wiki/Joint_Test_Action_Group

Ref: http://en.wikipedia.org/wiki/Joint_Test_Action_Group 利用FSM來判斷status,Mode select先選 Instruction Mode決定HardWare 內部要做怎樣的Mode,如現在是JTAG Debug Mode or Function Mode...等Mode 決定好時, 在下個Clock切換到Data Mode,開始打我們所要的Pattern,在此同時TDO會收到上一筆我們所要測的Result.

Ref: http://en.wikipedia.org/wiki/Joint_Test_Action_Group

Ref: http://en.wikipedia.org/wiki/Joint_Test_Action_Group

- 如果對JTAG Debug 有興趣的人,可以參考 http://urjtag.org/ 這裡面有已經開發好的Driver跟Debug,不過限制只有他內部提供的Board跟Cable有效.如果不是的,可能要自寫個Interface2Interface的Converter.

2010年2月24日 星期三

JTAG

訂閱:

張貼留言 (Atom)

沒有留言:

張貼留言