2010年3月28日 星期日

snake 4 Android

2010年3月26日 星期五

Path Delay Fault 4 ATPG Pt1

Pic Ref: http://www.wowcataclysminfo.com/wp-content/uploads/2009/09/wow-cataclysm-path-of-the-titans.jpg

Path Delay Fault :

Pic Ref: http://www.wowcataclysminfo.com/wp-content/uploads/2009/09/wow-cataclysm-path-of-the-titans.jpg

Path Delay Fault : sample case:

the red line is our critical path from input And1 to And3, the fast path is from And1 to And2, so in our methodology the violation may happen in gate Xor2.

sample case:

the red line is our critical path from input And1 to And3, the fast path is from And1 to And2, so in our methodology the violation may happen in gate Xor2.

Result :

http://sites.google.com/site/funningboy/perl_code/path_delay.rar?attredirects=0&d=1

2010年3月25日 星期四

Stuck at Fault 4 ATPG Pt2

- D Algorithm 底下是 D algorithm 的Sample, 主要分成 Propagate, Consistency. Propagate : 有點像是 Forward 的方式把Data Propagate 下去,直到我們的Flip -Flop端. 在經由我們的JTAG 做Debug的動作. Consistency: 像是Back Track的方式, 回頭去定義我們的Input vector. 底下的Sample中. 假設在Wire d被 Tied住成 0 (SA0), 如何用D algrithm找出解呢?

- Step1. 把 Wire d 的值先設成 "D", D表示 0->1 or 1->0的變化. 目前是 0->1. 因為被Tied 成 0, 所以我們要製造個1的Inf出來 可參考 http://funningboy.blogspot.com/2010/03/stuck-at-fault-4-atpg.html Step2. 在 Wire d的 Fanin 是由And(1)所給的, 所以在And 的Input端必須都要為1,才能確保 OutPut =1, Step3 . Progation 2 EndPoint, 為了要把 "D" 傳出去,在Nor(2)時的Control Point(Wire e) 必須要為0 Step4. Consistency 2 Input, 已知Wire e = 0 && Input B =1, 可以得到 NAND 的 Input C 為 1

演算法流程.

Propagate -> Up Date Look Up Table

+

Consistency -> Up Date Look Up Table

+

Rst

- Pic Ref: UMBC University

2 . Look Up Table Generator

透過C++ 產生Total Solutions. 假設有n個 inputs , 解空間就有 2^n 個.

3. Emulator (Tool)

PS: 本tool 請勿用在商業用途.

Language: C++.

Desgin Flow

Step 2. 準備好我們的IO.log存成 IO.log檔 0-> input 1 ->output IO.log 0 w1 0 w2 1 w9 1 w6 1 w11 EOF Step3. Look Up Table generator 在Pattern 資料夾下鍵入 %make, 會產生一個 Pattern.cpp的file ,這個file會把剛剛的Pattern1.v 轉成 C++的file. PS: 注意inpur output的前後關係,不然產生的Look up table會錯誤. Step4. Generator Look up table 在pattern 資料夾下鍵入 %g++ Pattern.cpp %./a.exe 會產生我們的 look up table 叫 GenPat.log

GenPat.log w1 w2 w3 w4 w5 w7 w6 w8 w9 w10 w11 0 0 0 0 1 1 1 0 0 1 0 1 0 0 0 1 1 1 0 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 1 0 1 1 1 1 1 0 0 EOF

Step5. 回到stuck\inc底下 在define.h 中會定義幾個參數.如Stuck at 的點, 跟Stuck at 的值,還有 Stuck at所要走的Path. #define StFLoc "w5" #define StFValue "0" #define StPath "Or1"

全部定義好後.在stuck資料夾下鍵入

%make

%./p1.exe

就ok了

執行結果

tool download

http://sites.google.com/site/funningboy/perl_code/stuck.rar?attredirects=0&d=1

tool download

http://sites.google.com/site/funningboy/perl_code/stuck.rar?attredirects=0&d=1

Stuck at fault 4 ATPG Pt1

Pic Ref : http://go2.wordpress.com/?id=725X1342&site=emilysutherland.wordpress.com&url=http%3A%2F%2Femilysutherland.files.wordpress.com%2F2009%2F12%2Fstuck.jpg

Pic Ref : http://go2.wordpress.com/?id=725X1342&site=emilysutherland.wordpress.com&url=http%3A%2F%2Femilysutherland.files.wordpress.com%2F2009%2F12%2Fstuck.jpg

- 底下我們針對ATPG (Auto Test Pattern Generator) 的 Stuck at fault 做出 Pattern Detected 的 Emulation 環境.

- Stuck at fault 簡介. 透過打入Pattern的方式,掃出我們IC中被Block 的部分,如VDD/Gnd short... 或者是接線被Tied死... 優點: 可以快速的驗證Design. 缺點: Stuck at Fault 在Real Time的Debug 上完全看不到Timing 所造成 Delay Fault.

- Propose and Case Study

底下先簡介一下,如何detected Fault.

在Step 1中 AND 閘, X,Y 分別為Input , Z為Output.

Z =X&Y.

Step 2中 如果AND 閘的Y端被 Gnd Tied住,導致Z永遠為 0,

所以我們試著去產生個1在Y端,讓Y能有1的訊號.如果這個1能被傳出去,

表示Design OK, 如果不能,表示Design 被Tied住.

除了要製造個1在Y端,還要確保Control Point(x)能夠把這個1傳出去,

而這個control point(x) 在AND閘時, x端需要一直Tied在 1的位置.

這樣 OutPut 的狀態只會受到Y的變化而改變.

- Fan in Extraction

透過DFS Search 紀錄每個走過的Node, 之後再根據每個Node的連接關係建立起一張Frame,

底下先用DFS 模擬出我們的Fain Path 有哪些, 在Step 1中,會定義我們的Path. 之後根據這些Path,依序插入每個Node的Inf, 如Delay, Area....

PS: Node = Gate,

Wire = Connection.

目前只考慮Node 的部分, Wire load Mode 目前是不考慮的.

Future: 可以根據這些Inf 做 Time Check, 跟Real Time 的(Simulation)驗證.

DFS 可參考 http://imfg.wordpress.com/2008/07/30/16/ 待續....

2010年3月21日 星期日

Face Book Happy Farmer analyer pt2

底下為Flash 的Variable.

version: "2.1",

firstPlay: "0",

uid: "xxxxxxxxxxx",

sig_user: "xxxxxxxxxx",

sig_session_key: "2.mQZTxp_jEsSSleEDweSIWA__.3600.1269417600-100000063194415",

sig_api_key: "xxxxxxxxxx",

host: "http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/",

web_base: "http://fbtwgw.farm.elex-tech.us/new_2_1_1/",

database: "http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/database/v0321/item.xml?4",

sig_time: "1269412560.3995",

mod: "facebook_tw",

farmuid:"xxxxxxx",

secretid: "xxxxxxx",

sig_ss:"Qay4KMXuZQymKSqjbCbdcw__",

sig_photo_upload:"0",

locale:"zh-tw",

appurl:"http://apps.facebook.com/farmgame_tw/",

ga_account:"UA-11729502-8",

invitefriendsURL:"http://apps.facebook.com/farmgame_tw/index.php?mod=friends",

//loadingPath:"http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/",

ga_path:http://img.harvest.6waves.com/farmgame_tw/static/swf2/tongji/library.swf

底下為Flash 的Variable.

version: "2.1",

firstPlay: "0",

uid: "xxxxxxxxxxx",

sig_user: "xxxxxxxxxx",

sig_session_key: "2.mQZTxp_jEsSSleEDweSIWA__.3600.1269417600-100000063194415",

sig_api_key: "xxxxxxxxxx",

host: "http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/",

web_base: "http://fbtwgw.farm.elex-tech.us/new_2_1_1/",

database: "http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/database/v0321/item.xml?4",

sig_time: "1269412560.3995",

mod: "facebook_tw",

farmuid:"xxxxxxx",

secretid: "xxxxxxx",

sig_ss:"Qay4KMXuZQymKSqjbCbdcw__",

sig_photo_upload:"0",

locale:"zh-tw",

appurl:"http://apps.facebook.com/farmgame_tw/",

ga_account:"UA-11729502-8",

invitefriendsURL:"http://apps.facebook.com/farmgame_tw/index.php?mod=friends",

//loadingPath:"http://img.harvest.6waves.com/farmgame_tw/static/swf_2_1/",

ga_path:http://img.harvest.6waves.com/farmgame_tw/static/swf2/tongji/library.swf

Sample version 1 功能: 登入FaceBook, 載入農場資訊 Export 2 Local host 請更改 my $email = 'xxxx@gmail.com'; my $pass = 'xxxx'; 執行後會產生 test.html. 點入 test.html 就會裝載 開心農場到 Local 端 執行結果 如上圖 Code Download http://sites.google.com/site/funningboy/perl_code/farmer.pl?attredirects=0&d=1

FaceBook Happy Farmer analyser Pt1

PS: 本教程只提供學術交流,請勿用於破壞or改變原程式設定.

Tool: WireShark + Perl + OpenSLL + Cygwin

WireShark : 做封包分析, 解析我們送出的"封包"跟實際要送的"封包"是否相同.

WireShark 教程可參考

http://blog.shaolin.tw/2008/03/wireshark.html

Perl : 為我們的程式語言

裡面用到的 Lib

use strict;

use WWW::Mechanize;

use HTTP::Cookies;

use HTML::Parse;

可參考

http://search.cpan.org/~petdance/WWW-Mechanize-1.60/lib/WWW/Mechanize.pm

http://search.cpan.org/~gaas/libwww-perl-5.834/lib/LWP/UserAgent.pm

Cygwin: 模擬環境(IDE)

http://www.cygwin.com/

OpenSLL: 為我們加密要用的軟體

http://csc.ocean-pioneer.com/docum/ssl_basic.html

下載安裝: http://www.openssl.org/source/

請下載bin 檔,就不需要重新compiler

Step(1)

先打開WireShark開始抓取封包

capture->interface->broadcom....(選有IP的)->start

就會開始抓取"封包"

PS: 本教程只提供學術交流,請勿用於破壞or改變原程式設定.

Tool: WireShark + Perl + OpenSLL + Cygwin

WireShark : 做封包分析, 解析我們送出的"封包"跟實際要送的"封包"是否相同.

WireShark 教程可參考

http://blog.shaolin.tw/2008/03/wireshark.html

Perl : 為我們的程式語言

裡面用到的 Lib

use strict;

use WWW::Mechanize;

use HTTP::Cookies;

use HTML::Parse;

可參考

http://search.cpan.org/~petdance/WWW-Mechanize-1.60/lib/WWW/Mechanize.pm

http://search.cpan.org/~gaas/libwww-perl-5.834/lib/LWP/UserAgent.pm

Cygwin: 模擬環境(IDE)

http://www.cygwin.com/

OpenSLL: 為我們加密要用的軟體

http://csc.ocean-pioneer.com/docum/ssl_basic.html

下載安裝: http://www.openssl.org/source/

請下載bin 檔,就不需要重新compiler

Step(1)

先打開WireShark開始抓取封包

capture->interface->broadcom....(選有IP的)->start

就會開始抓取"封包"

這邊我們先確定好登入的位置.

打入"帳號","密碼"看返回的Page. 登入的Type : http Port(80)

http://apps.facebook.com/farmgame_tw/index.php

確定能登入上 FaceBook 的開心農場.

切換到好友List,找個能偷採的人.....就偷採幾個sample看看封包是回傳怎樣的Data.

得知這些Inf後,Stop WireShark. 在WireShark 的 Filter: 中鍵入http,找出我們所要的data,其它的封包就可忽略.

Step(2)

找在 Http底下 尋找 post 的 method

Name: "POST /v3/data/gateway.php HTTP/1.1" 這個封包, 按右鍵 -> follow TCP stream

會看到下圖

紅色是我們Post出去的reguest.

藍色是我們接收到的"封包"

這邊我們先確定好登入的位置.

打入"帳號","密碼"看返回的Page. 登入的Type : http Port(80)

http://apps.facebook.com/farmgame_tw/index.php

確定能登入上 FaceBook 的開心農場.

切換到好友List,找個能偷採的人.....就偷採幾個sample看看封包是回傳怎樣的Data.

得知這些Inf後,Stop WireShark. 在WireShark 的 Filter: 中鍵入http,找出我們所要的data,其它的封包就可忽略.

Step(2)

找在 Http底下 尋找 post 的 method

Name: "POST /v3/data/gateway.php HTTP/1.1" 這個封包, 按右鍵 -> follow TCP stream

會看到下圖

紅色是我們Post出去的reguest.

藍色是我們接收到的"封包"

待續....

待續....

Eclipse + SystemC + Cygwin

SC_MODULE(fir) {

sc_in; reset;

sc_in<bool> input_valid;

sc_in<int> sample;

sc_out<bool> output_data_ready;

sc_out<int> result;

sc_in_clk CLK;

sc_int<9> coefs[16];

SC_CTOR(fir)

{

SC_CTHREAD(entry, CLK.pos());

reset_signal_is(reset,true);

#include "fir_const.h"

}

void entry();

};

在 fir.cpp中, 會定義這個Black Box的動作,底下是16個tap的Fir.

hw 的架構大概如此, 底下是5個tap 的FIR

Pic Ref: http://commons.wikimedia.org/wiki/File:Fir_filter_df1.png

這邊會用wait()去模擬HW的Delay.

Pic Ref: http://commons.wikimedia.org/wiki/File:Fir_filter_df1.png

這邊會用wait()去模擬HW的Delay.

void fir::entry() {

sc_int<8> sample_tmp;

sc_int<17> pro;

sc_int<19> acc;

sc_int<8> shift[16];

// reset watching

/* this would be an unrolled loop */

for (int i=0; i<=15; i++)

shift[i] = 0;

result.write(0);

output_data_ready.write(false);

wait();

// main functionality

while(1) {

output_data_ready.write(false);

do { wait(); } while ( !(input_valid == true) );

sample_tmp = sample.read();

acc = sample_tmp*coefs[0];

for(int i=14; i>=0; i--) {

/* this would be an unrolled loop */

pro = shift[i]*coefs[i+1];

acc += pro;

};

for(int i=14; i>=0; i--) {

/* this would be an unrolled loop */

shift[i+1] = shift[i];

};

shift[0] = sample_tmp;

// write output values

result.write((int)acc);

output_data_ready.write(true);

wait();

};

}

執行結果.

2010年3月20日 星期六

System Level - SystemC

SystemC 是以C++為基礎,並加入Hw synchronous/asynchronous/event trigger 的概念進去.

TLM (Transaction Level Model 0)

http://www.eettaiwan.com/ART_8800316267_480102_TA_5a6d92f3.HTM

Module : Black Box Name

Port : 接口 In/Out/InOut bit

SystemC 是以C++為基礎,並加入Hw synchronous/asynchronous/event trigger 的概念進去.

TLM (Transaction Level Model 0)

http://www.eettaiwan.com/ART_8800316267_480102_TA_5a6d92f3.HTM

Module : Black Box Name

Port : 接口 In/Out/InOut bit

WretchXD analyser

在按F9又接回return 的地方.似乎找不到任何JMP資訊,也沒有任何關鍵字.

Step (2).

跳出OllyICE,在重新載入.不做run(F9)的動作.

做關鍵字收尋. 按右鍵 Search for -> All referenced string text.

(1). Key word "password" 找不到 .

"passwd" 找到摟, 記錄一下斷點資訊,跟所在的記憶體位置(0X004092F8),

判斷此記憶體的位置是否會Post到不該連上的Web.

(2). 依序向下收尋,看有沒有access這段記憶體位置

跳出 All referrnced string text,回到原本的地方, 改用constant收尋來查找.

Search for -> all constants 鍵入004092f8 (Hex)就會找出所有有用到這段記憶體區段有關的指令.

發現只有找到一個

0042294D . 68 F8924000 push 004092F8; UNICODE "&passwd="

表示只有這個地方會抓 Passwd 到某個地方,在根據這個位置往上/下找,判斷是做怎樣的動作.

在按F9又接回return 的地方.似乎找不到任何JMP資訊,也沒有任何關鍵字.

Step (2).

跳出OllyICE,在重新載入.不做run(F9)的動作.

做關鍵字收尋. 按右鍵 Search for -> All referenced string text.

(1). Key word "password" 找不到 .

"passwd" 找到摟, 記錄一下斷點資訊,跟所在的記憶體位置(0X004092F8),

判斷此記憶體的位置是否會Post到不該連上的Web.

(2). 依序向下收尋,看有沒有access這段記憶體位置

跳出 All referrnced string text,回到原本的地方, 改用constant收尋來查找.

Search for -> all constants 鍵入004092f8 (Hex)就會找出所有有用到這段記憶體區段有關的指令.

發現只有找到一個

0042294D . 68 F8924000 push 004092F8; UNICODE "&passwd="

表示只有這個地方會抓 Passwd 到某個地方,在根據這個位置往上/下找,判斷是做怎樣的動作.

會發現一堆的regular expression,

0041DD1F . BA 108D4000 mov edx, 00408D10; UNICODE "

會發現一堆的regular expression,

0041DD1F . BA 108D4000 mov edx, 00408D10; UNICODE "2010年3月19日 星期五

Wretch Catcher

- 無名抓圖Sample Case....

- Environment : Cygwin + Perl PS: 為Smaple 版, (1)沒GUI. (2)沒有Page Check 的機制, 只能抓Page 1的圖. (3)沒有解鎖的功能. (4)相本命名以數字為主. (5)影像檔請自行改檔名. (6)不支援multi thread

- Yahoo Photo Link 機制 假設底下是我們一般在瀏覽器看到的Link. http://www.wretch.cc/album/show.php?i=hellokysi&b=42&f=1240850068&p=14 在圖形上按右鍵-> 內容 會顯示這張Photo的Real Link http://f4.wretch.yimg.com/hellokysi/42/1240850068.jpg?0OEuLMlDdhIDGTsoUySqfRQRWxhNzN9y8RzcElkwroa9TFsnfKQCg66zCCX9y_t1IF4- 所以我們大概可以知道 Photo 所存在的路徑在這個資料夾下 http://f4.wretch.yimg.com/hellokysi/42/1240850068.jpg? 但是後面又接了一大串的驗證檔,這是Yahoo 怕駭客一直access主機所設定的驗證機制.會Check cookie是否存在. 如果不存在回傳回403 Error. 所以我們在code中要設定我們的cookie路徑.

- Design Flow Step1. Find the "xx帳號" 所有的Alum List Step2. 根據Alum 的ID, 依序進入Alum中 Step3. 在Alum中找Photo Link Step4. 在Photo Link 中找 Real 路徑 Step5. 轉mode bin mode -> utf8 mode

- 執行結果

- 請改 wretch.pl 中的"帳號"設定. my $GbWebInf='http://www.wretch.cc/album/cuteyo88'; code download http://sites.google.com/site/funningboy/perl_code/wretch.pl?attredirects=0&d=1

2010年3月18日 星期四

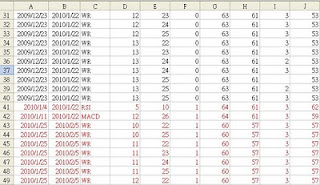

Auto Indicator 4 Excel

Pic Ref: http://www.bloggingstocks.com/tag/economic+indicators/

Pic Ref: http://www.bloggingstocks.com/tag/economic+indicators/

- 簡易的轉檔程式 支援 KD, RSI, SAR, K, MACD, OBV, PSY.... 可自行定義每個指標的Length

- 工具: Perl, Excel

PS: 在 stock(sheet)底下, 請按變更圖表類型,改成股票圖.

- 請先用DDE抓好Stock Data DDE下載請參考 http://funningboy.blogspot.com/2010/02/trading-performance-v1.html http://funningboy.blogspot.com/2010/02/trading-performance-v2.html code Download http://sites.google.com/site/funningboy/perl_code/indicator.rar?attredirects=0&d=1

- 執行結果

使用方式

Future teller Pt2

Pic Ref: http://blog.northstarmanifesto.com/2009/01/the-emerging-future/

Pic Ref: http://blog.northstarmanifesto.com/2009/01/the-emerging-future/

- 接續 Future teller Pt1 http://funningboy.blogspot.com/2010/03/futuer-teller.html

- 所以我們會得到sample的解 Day D(1) D(2) D(3) D(4) D(5) D(6) D(7) Dif 3% -> -1% -> 0% -> 1% -> 0% -> %3 -> 1% PS: 注意,此解必須符合我們的Constrain.

- 帶入機率函數求解 前提: 不考慮每日的機率變動率. 每日的機率值是固定的, P(1%) = Constant Value, 不是 P1(1%) for Day(1) p2(1%) for Day(2)...

- Static Part StP = P(3%)*P(-1%)*P(0%)*P(1%)*P(0%)*P(3%)*P(1%)

- Dynamic Part DmP = P(3% -> -1%)*P(-1% -> 0%)*P( 0% -> 1%)*P( 1% -> 0%) *P( 0% -> 3%)*P( 3% -> 1%)

- Dynamic + Static SDP = P(3%)*P(3% -> -1%)*P(-1%)*P(-1% -> 0%).....

- Flow Chart 找出所有的解空間, 在對每個解空間做排列的動作,之後在帶入Probability.

PS: 可以而外增加Constrain 變數. 如

7% -> -7%, 我想如果這種機率應該是很難發生吧.

Or 加入連續下跌的Constrain

-3% -> -3% Drop

- 結果 T :: 1 ==Total Prob(Dym + St==)0.001 T :: 2 ==Total Prob(Dym + St==)0.00212 T :: 3 ==Total Prob(Dym + St==)0.00331718 T :: 4 ==Total Prob(Dym + St==)0.00602681 T :: 5 ==Total Prob(Dym + St==)0.00723811 T :: 6 ==Total Prob(Dym + St==)0.00994943 T :: 7 ==Total Prob(Dym + St==)0.0111607 T :: 8 ==Total Prob(Dym + St==)0.0138721 code / Rst download http://sites.google.com/site/funningboy/perl_code/expect.rar?attredirects=0&d=1

2010年3月17日 星期三

Futuer Teller pt1

Pic Ref: http://www.istockphoto.com/stock-photo-4978052-fortune-teller-with-glowing-crystal-ball.php

Pic Ref: http://www.istockphoto.com/stock-photo-4978052-fortune-teller-with-glowing-crystal-ball.php

- 底下用機率學的方式來推算出在有限時間下,能達到目標獲利的期望值.

- 先以底下的圖當例子.如果把股價的Time Frame展開, 因為漲跌幅的限制,我們每天能走的步數大概如(1) 所示,每個unit代表股價的漲跌幅. Sample Case 目標: 我們現在要估計未來 10天內我們可以獲利7%的機率有多高? 定義/假設: Dynamic Probability(動態變動率) 為股價變動的機率, 如 P(漲%1 -> 漲%3), P(漲%1 -> 平盤)..... Static Probablity(靜態變動率) P(漲%1), P(平盤)..... PS: 我們會分別定義每種狀態的機率.以台股有漲跌幅限制的情況下.我們先分成 1%, 3%, 5%, 7%, 0%, -1%, -3%, -5%, -7%的狀態機. PS: 如果漲幅為 M(2%) if(3%>M && M >=1%){ M=1% } 我們會Translate 2 Our definition P(1%) = 0.4, P(%3) =0.2 ..... (Static Probability) P(1%->3%) =0.2 , P(1%->0%) =0.3 .... (Dynamic Probability) 最後統計 Static, Dynamic, Static + Dynamic的機率分別有多少.

- Sample 4 Entry Case Constrain: T<=10; //進場之後,我們最大所能持股的時間. P=7; //獲利目標7%之後出場. Soluation: Find the Path to Meet the Constrain Step1. 先以我們進場點(Entry Point)為中心做Unit展開. Step2.假設D(1)收盤價比我們(Entry Point)來的高3%,就往右走3個unit. Update我們的Cur Bar紀錄現在的位置. Step3. 假設D(2)的收盤價比D(1)的小1%,我們就往左走1個unit. ..... StepN. 直到我們的Constrain Meet. 所以我們可以找到底下Sample的組合 Day D(1) D(2) D(3) D(4) D(5) D(6) D(7) Dif 3% -> -1% -> 0% -> 1% -> 0% -> %3 -> 1% Tot 3% -> 2% -> 2% -> 3% -> 3% -> %6 -> 7%

待續....

2010年3月15日 星期一

Eclipse + CDT + Perl

- Eclipse 有在做程式開發的人應該很熟悉,主要用在跨平台的自由式整合開發環境(IDE). 不需要每套軟體都要一個開發環境,用 Eclipse Plus的功能,把Device, class, application,加入進來, 透過這個平台來連接不同的Interface.

- Eclipse + java 請參考 http://www.javaworld.com.tw/jute/post/view?bid=10&id=40626 Eclipse + CDT (gcc/g++) 請參考 http://www.javaworld.com.tw/jute/post/view?bid=10&id=53262&sty=1&tpg=1&age=0 PS: 請注意, 如果要用MinGw當compiler時,要把 mingw32-make.exe改成Eclipse 所認得的make. (改變Eclipse的compiler Path 改成 mingw32-make.exe) Eclipse 基礎 http://www.javaworld.com.tw/jute/post/view?bid=10&id=87494&sty=1&tpg=1&age=0

- Eclipse + perl

請參考

http://www.epic-ide.org/

目前開發環境

Cygwin + Eclipse CDT + Perl + MinGw32

安裝完成可以用 window->preferences check Perl是否安裝完成.

USB Device

- Pic Ref: http://www.geekalerts.com/usb-missile-launcher-with-webcam/

- 上圖是我在找Usb Driver時看到的Application,呵呵...不知道準不準就是.

- 拉回主題. 底下用Usb Lib來做到Remote Control or Device Configure. 可應用的範圍有 JTAG debug, Erase Flash..... 可參考 Print Port Control 2 JTAG control http://funningboy.blogspot.com/2010/02/print-port-control.html http://funningboy.blogspot.com/2010/02/jtag.html

- 準備工具

libusb-win32

http://libusb-win32.sourceforge.net/

安裝流程就請參考底下

download, 且安裝

libusb-win32-filter-bin-0.1.12.2.exe

底下有個測試程式,會幫你Detected 目前的Usb Device, Test Program

下載測試檔

libusb-win32-device-bin-0.1.12.2.tar.gz

這邊會有compiler好的Dll, 跟Driver, 把bin/libusb0.dll 放到 windows/system32 底下,

libusb0.sys 放到 windows/system32/driver底下.

Cygwin + Mingw( cross compiler)

Cygwin為模擬Linux的環境, Mingw 為Windows 的 gcc/g++ compiler. 雖然Cygwin 內建有 gcc/g++ compiler,但是那個是針對Linux Based的.我們現在是用Cygwin 來模擬Linux環境, 實際再run的時候, 最底層的Protocl 還是Windows Based, Cygwin 只是個Wrapper用 DLL來溝通.

安裝流程

下載Cygwin (略過) 請記的環境變數 Path的部分要加入系統變數中

Default : /usr/local/bin:/usr/bin:/bin:/usr/X11R6/bin..

可鍵入

% echo $PATH

確定gcc / g++ version

% gcc -v

確保Mingw 的Path 有被安裝進去

Ref : http://www.mingw.org/wiki/FAQ

PS: 如果你要自己compiler 出DLL檔的話, 可以下載src 資料夾.

libusb-win32-src-0.1.12.2.tar.gz

解壓之後,把makefile內的 -mno-cygwin 拿掉, 雖然 -mno-cygwin 會告訴gcc/g++ 現在是用Mingw來當compiler, 但是我用這個指令時會fail. 之後就鍵入

%make

....

會產生 libusb0.dll, libusb0.sys ....

就我們之前用Binary安裝的檔案.

下載測試檔

libusb-win32-device-bin-0.1.12.2.tar.gz

這邊會有compiler好的Dll, 跟Driver, 把bin/libusb0.dll 放到 windows/system32 底下,

libusb0.sys 放到 windows/system32/driver底下.

Cygwin + Mingw( cross compiler)

Cygwin為模擬Linux的環境, Mingw 為Windows 的 gcc/g++ compiler. 雖然Cygwin 內建有 gcc/g++ compiler,但是那個是針對Linux Based的.我們現在是用Cygwin 來模擬Linux環境, 實際再run的時候, 最底層的Protocl 還是Windows Based, Cygwin 只是個Wrapper用 DLL來溝通.

安裝流程

下載Cygwin (略過) 請記的環境變數 Path的部分要加入系統變數中

Default : /usr/local/bin:/usr/bin:/bin:/usr/X11R6/bin..

可鍵入

% echo $PATH

確定gcc / g++ version

% gcc -v

確保Mingw 的Path 有被安裝進去

Ref : http://www.mingw.org/wiki/FAQ

PS: 如果你要自己compiler 出DLL檔的話, 可以下載src 資料夾.

libusb-win32-src-0.1.12.2.tar.gz

解壓之後,把makefile內的 -mno-cygwin 拿掉, 雖然 -mno-cygwin 會告訴gcc/g++ 現在是用Mingw來當compiler, 但是我用這個指令時會fail. 之後就鍵入

%make

....

會產生 libusb0.dll, libusb0.sys ....

就我們之前用Binary安裝的檔案.

- 結果 在libusb-win32-src-0.1.12.2底下有個tests的資料夾,用裡面的sample當例子 鍵入 %gcc -O2 -Wall -o DLSPD.exe -I./src testlibusb.c -s -L. -lusb -lgdi32 -luser32 -lcfgmgr32 -lsetupapi -lcomctl32

最後就是要K API摟....

Ref: http://dannynote.blogspot.com/2008/11/linuxlibusblibrarylinuxusbkernel-device.html

http://realchecko.blogspot.com/2009/04/build-openocd-under-mingw-with-ftd2232.html

最後就是要K API摟....

Ref: http://dannynote.blogspot.com/2008/11/linuxlibusblibrarylinuxusbkernel-device.html

http://realchecko.blogspot.com/2009/04/build-openocd-under-mingw-with-ftd2232.html

2010年3月12日 星期五

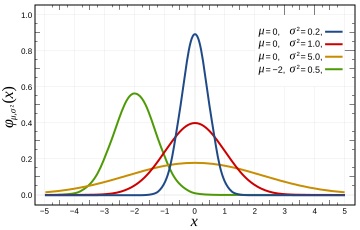

Normal Distribution

Pic Ref: http://en.wikipedia.org/wiki/Normal_distribution

Pic Ref: http://en.wikipedia.org/wiki/Normal_distribution

- 目標: 利用常態分部曲線,算出每日的支撐壓力 "價", "量".

- 假設 : 在每日的成交量跟價會呈現"常態式"的分部,以底下的紅K做例子.在實心的部分表是大家所願意購買的支撐價,相對的成交量也較集中於此,而在最高價.最低價的分部就會被忽略.

可以用積分的方式算出底下藍色的面積,佔今天成交量的幾成,就可以大概推算出買賣量的位置.

PS: 積分可以用Discrete的方式做累加,只要取的區間越小就越像是Continuois的積分型態.

- 準備工具. Cygwin Environment (IDE) g++/Mingw32 (Compiler) Boost (Boost Lib) GnuPlot (Plot Result) 模擬環境 + compiler Cygwin + g++ install http://cygwin.com/ C++ Extend Library Boost install http://www.fischerlaender.net/development/using-boost-c-libraries-with-gcc-g-under-windows GnuPlot 繪圖工具 http://www.gnuplot.info/

- 常態分部算法, 我們就先用每日的 Open, High, Low, Close當作Sample. 先算出Mean = (Open + High + Low + Close)/4, 在算出 Deviation = sqrt( 1/N*(Xi -Xmean)^2 , 2 ). 之後再根據積分函數算出成支撐面積,這邊我們就用最簡單的方式,用線性的內差法,來取代積分函數,根據Normal Distribution定理下,指要落在一個正負標準差內,就佔全體的60%,正負兩個標準差內佔了90%,在用Approach的方式算出今日成交的支撐價跟量. Ref : http://en.wikipedia.org/wiki/Normal_distribution

- Test Case 1101.TW http://sites.google.com/site/funningboy/perl_code/1101.TW.csv?attredirects=0&d=1 結果下載 http://sites.google.com/site/funningboy/perl_code/normaldistribution.xlsx?attredirects=0&d=1 sample code http://sites.google.com/site/funningboy/perl_code/Nm4Stock.cpp?attredirects=0&d=1 command % g++ -c -I/usr/include/boost-1_33_1/ -o Nm4Stock.o Nm4Stock.cpp % g++ -o Nm4Stock.exe Nm4Stock.o % ./Nm4Stock.exe > xxx.csv

2010年3月11日 星期四

NSGA II

- Multi Object Optimization(多目標最佳化),在現實世界中我們要最佳化的目標可能不只有一個,最簡單的例子就是風險跟獲利,兩者是互相Trade off的因子,如果要高獲利想對的風險也較高,如何能找到高獲利低風險的因子,就必須透過Multi Object Optimization來做. 底下可以參考我之前做的 GA Optimization,對每個指標的Length做最佳化,找出最好的進出場時間. http://funningboy.blogspot.com/2010/02/trading-performance-v1.html http://funningboy.blogspot.com/2010/02/trading-performance-v2.html

- 底下就Model而言定義出我們Optimization的因子 風險因子: 簡單的說就是 Risk = E[x,t+1] -C[x,t], E[x,t+1]為我們預期T+1的獲利,C[x,t]為現在收盤價Constant Value.可以想成如果E[x,t+1] =~ C[x,t],表示我們預測的準確性高,相對的風險因子也較低. PS: 為未來預期結果. 獲利因子: PS: 為現在結果

2010年3月10日 星期三

Time Windows

Pic Ref : http://dckaleidoscope.files.wordpress.com/2009/03/clock.jpg

Pic Ref : http://dckaleidoscope.files.wordpress.com/2009/03/clock.jpg

- 相信Time是大家所最Care的因素吧. 底下就來大概介紹一下如何藉由Time Frame的方式來達到最好的獲利.

- 前提: 在Market的市場中,每日的開盤到收盤的時間是連續的,但是就以"天","月"的觀點來看,變成是種不連續的訊號,所以才會有K線的指標出現. 假設: 在此前提下,我們假設每天的訊號是不連續的,我們用Time Frame來表示這些訊號,藉由Time Frame 的前後移動推斷出T-n or T+n的趨勢分析, 主要概念還是藉由"SAR" 的技術指標的延伸.利用翻"多"或者是翻"空"的情況來增加或減少我們持股的時間. SAR Ref: http://www.ezchart.com.tw/inds.php?IND=SAR PS: 因為金融市場的未來性不能被預期,如何降低持有股票的風險性相對的很重要,透過Time的時間軸,來達到Filter的效用.

- Flow: EP : Entry Price CP : Current Price (Close/Lowest) LT : LiftTime (持股時間) UT : Up Band LiftTime (最久持股時間) LT : Low Band LiftTime (最短持股時間) Dif : LiftTime Inc/Sub (翻多還是翻空的Default unit) Sample code #Initial $LT =50; $UT = 60; $LT =40; #Method if ( $CP >=$EP ){ $LT+=$Dif; } //如果Curent Price比我們 Entry Price 高,就延長LifeTime else{ $LT-=$Dif; } // 反之減少 LifeTime if( $LT == $UT $LT == $LT){ Call Sell(); // 當LifeTime 達到我們的Constrain後就出場. }

PS: 可以改變 "Dif" 的參數,可以加入 成交量或者K線的大小....,變成一種Discrete的方式.如下 HP : Highest Price. LP : Lowest Price. $Dif = 2 ($HP-$LP)/($HP+$LP) <= 0.3 = 1 ($HP-$LP)/($HP+$LP) <= 0.1

.... 可以自行發揮.

2010年3月9日 星期二

Max Drop Down test

- 這是我突然想到的測試方式,藉由這次的大盤下跌,測試技術指標是否能夠優先避開下跌的波段,等頭部確定後再做回補的動作.

- 前提: 利用GA Algorithm 做出每個技術指標的進出時間點 可以參考底下我做過的Research http://funningboy.blogspot.com/2010/02/trading-performance-v1.html http://funningboy.blogspot.com/2010/02/trading-performance-v2.html 假設: Case 4 2303.TW Simulation Test Time : 2010/03/08 (T-50) Constrain : Initial Poluation =30; End Poluation Size =500; End Generation =10; Limit Fitness =2; MutationRate =0.1; PS : 內部加入 Time Windows && Profit Filter, KD, RSI, MACD, WR, DMI, OBV, VR, SAR, BIAS. Time Windows http://funningboy.blogspot.com/2010/03/time-windows.html 初始產生30組基因解,且收斂範圍為10個世代 or Poluation大小到達500組,每組基因至 少要獲利2,且變異機率為0.1. Entry Rule: 我們會建立每個技術指標的 Fast , Slow 線,藉由Fast 跟 Slow的交叉做逼近的動作,找出 進場出場位置,在這就不詳述了. 假設KD進出場策略,請參考底下 http://funningboy.blogspot.com/2010/02/trading-performance-v1.html

- Rst 表格欄位依序為 EntryTime,LeaveTime,Indicator,FastLength,SlowLength,Buy/Sell,EntryPrice,LeavePrice ,Profit,LifeTime PS: Buy/Sell 0/1 發現再大跌時我們會翻空手,且還有 ">" 2 的獲利情形,之後到2010/02/04時又轉回多手的狀態.可以做多也可以做空.

結論: 發現在WR, OLB, BIAS 對2330.TW 的進出有良好的績效,且WR 在多轉空,空轉多

時也能維持良好的獲利.

PS: 我個人認為每檔股票都有其相對應的技術指標,就像操作原油,黃金....,每樣商

品都有其特殊的地方. 如何發現商品的特性,不外藉由不斷的測試跟Time

Moving,找每一季所對應的symptom...

結論: 發現在WR, OLB, BIAS 對2330.TW 的進出有良好的績效,且WR 在多轉空,空轉多

時也能維持良好的獲利.

PS: 我個人認為每檔股票都有其相對應的技術指標,就像操作原油,黃金....,每樣商

品都有其特殊的地方. 如何發現商品的特性,不外藉由不斷的測試跟Time

Moving,找每一季所對應的symptom...

Rst Download: http://sites.google.com/site/funningboy/stock_data/2010_02_2303_Ga_Rst.xls?attredirects=0&d=1

http://sites.google.com/site/funningboy/stock_data/2010_02_2303_Ga_Rst?attredirects=0&d=1

FANN Neural Networks pt1

Pic Ref : http://www.stepchange.no/

Pic Ref : http://www.stepchange.no/

- Neural Networks (類神經網路), 透過學習跟分析來解決非線性的工程問題,一般用在最佳化理論,跟人工智慧上. Ref: http://en.wikipedia.org/wiki/Neural_network

- 在此我們利用FANN Neural Network的基礎,來解決金融商品上的價錢預測,或者是透過歷史資料的學習分析,找出適當的進出場價格. Target: (1)藉由類神經演算法的學習跟預測的功能來推得T+1~T+N天的模擬結果. Target: (2)利用feedback運算把預測值跟實際當天收盤價做比對,做誤差性質的量化分析.

- Basic Flow

主要分成 3 個 Layer. 分別是 Input Layer, Hidden Layer, OutPut Layer.

Input Layer : 為我們的Input Inf,

Hindden Layer: 為decided, 判斷決策.

Output Layer : 為Out Data.

以底下的Sample 為例. 在Hidden Layer中的 H1, 它的Input 來自 X1, X2, X3, X4. Ouput 為Z1, 所以我們可以表示成 H1 = C1*X1 + C2*X2 + C3*X3 + C4*X4, C1~ C4 分別為 Cofactor(Weight),來決定每個input的權重. 在來決定output 的Direction

Z1 =1; H1 ">="30

Z2 =0; H1 "<" 30 當H1 的Rrank ">=" 30, Output 就傳給 Z1, 相反的傳給Z2....

以底下的Sample 為例. 在Hidden Layer中的 H1, 它的Input 來自 X1, X2, X3, X4. Ouput 為Z1, 所以我們可以表示成 H1 = C1*X1 + C2*X2 + C3*X3 + C4*X4, C1~ C4 分別為 Cofactor(Weight),來決定每個input的權重. 在來決定output 的Direction

Z1 =1; H1 ">="30

Z2 =0; H1 "<" 30 當H1 的Rrank ">=" 30, Output 就傳給 Z1, 相反的傳給Z2....

Pic Ref : http://www.information-management.com/specialreports/2008_61/10000704-1.html

Pic Ref : http://www.information-management.com/specialreports/2008_61/10000704-1.html

- 底下先用最簡單的範例 XOR來做實驗

table Ref : http://nxforce.blogspot.com/search/label/ANN

用數學公式表示法

table Ref : http://nxforce.blogspot.com/search/label/ANN

用數學公式表示法

簡單的說就是透過Hidden Layer的層數跟學習係數一直做Recursive的動作,算出Input跟Output的誤差,透過誤差值的調整Weight,讓Output的值最後能達到收斂狀態.所以我們就可以很明確的畫出True, False落在的的區間.在藉由這些Inf 反推回 Input 跟 Output的關係.

smaple 圖示

http://www.openprocessing.org/visuals/?visualID=159

簡單的說就是透過Hidden Layer的層數跟學習係數一直做Recursive的動作,算出Input跟Output的誤差,透過誤差值的調整Weight,讓Output的值最後能達到收斂狀態.所以我們就可以很明確的畫出True, False落在的的區間.在藉由這些Inf 反推回 Input 跟 Output的關係.

smaple 圖示

http://www.openprocessing.org/visuals/?visualID=159

- Ref : http://leenissen.dk/fann/