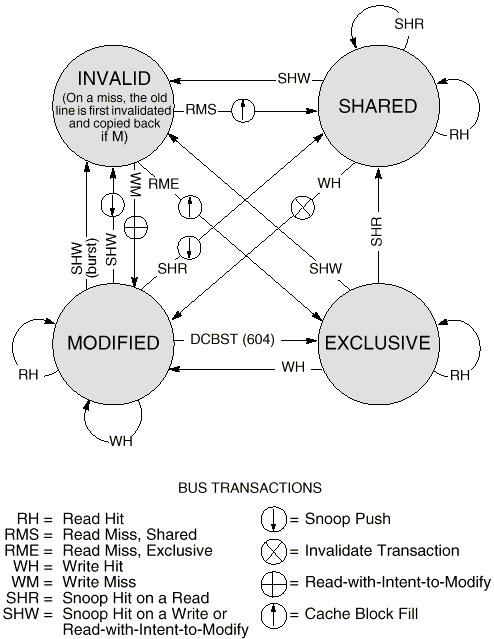

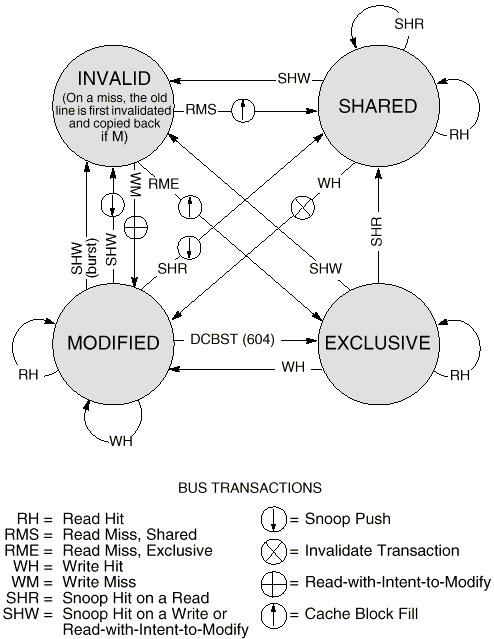

在傳統 single core 下, Cache 只需要考慮 hit/miss 的狀態.但進入 multi cores 的世代, Cache 除了要考慮 hit/miss 之外,還要考慮是否是Share memory part or local(private) memory part. 所以Intel 提出了 MESI 的架構來解決share memory data read/write 的問題.

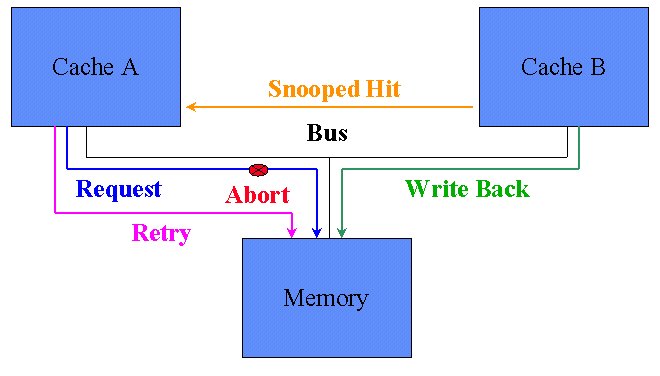

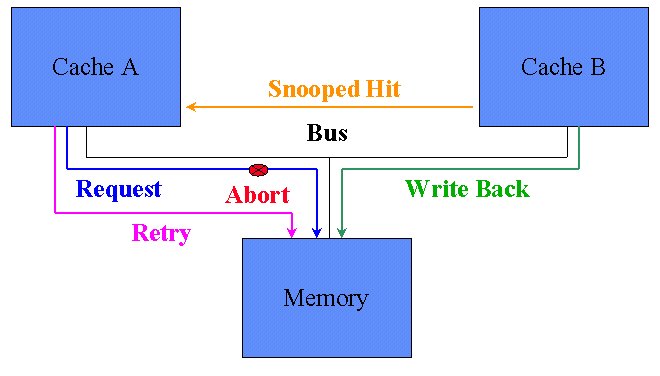

其實想法很簡單, 如果是share part的部份.有write update 就 broadcast 出去,叫其他的 Cache update, 順便把data 寫回 memory, 如果是 read update 就只要 update 自己本身的 Cache 就好.

底下我們用sample emulator 來實現 MESI 的架構.

constrains:

CPU 的 schedule 為已知, 避免同時有兩個CPU 的 race condition.

cache 架構不是正式的 tags,block, valid. 只有考慮 address 跟 valid 的判斷.

有興趣的人可以抓來玩玩. ^_^

download

here.

Refs:

Memory part 2: CPU caches

Cache工作原理-5

Cache Coherence

CMP中Cache一致性协议的验证

Optimizing the MESI Cache Coherence Protocol for Multithreaded Applications on Small Symmetric Multiprocessor System

Cache is King -or- Things are about to get MESI

MESI Cache Coherency Protocol

在傳統 single core 下, Cache 只需要考慮 hit/miss 的狀態.但進入 multi cores 的世代, Cache 除了要考慮 hit/miss 之外,還要考慮是否是Share memory part or local(private) memory part. 所以Intel 提出了 MESI 的架構來解決share memory data read/write 的問題.

在傳統 single core 下, Cache 只需要考慮 hit/miss 的狀態.但進入 multi cores 的世代, Cache 除了要考慮 hit/miss 之外,還要考慮是否是Share memory part or local(private) memory part. 所以Intel 提出了 MESI 的架構來解決share memory data read/write 的問題.

其實想法很簡單, 如果是share part的部份.有write update 就 broadcast 出去,叫其他的 Cache update, 順便把data 寫回 memory, 如果是 read update 就只要 update 自己本身的 Cache 就好.

底下我們用sample emulator 來實現 MESI 的架構.

constrains:

CPU 的 schedule 為已知, 避免同時有兩個CPU 的 race condition.

cache 架構不是正式的 tags,block, valid. 只有考慮 address 跟 valid 的判斷.

有興趣的人可以抓來玩玩. ^_^

download here.

Refs:

Memory part 2: CPU caches

Cache工作原理-5

Cache Coherence

CMP中Cache一致性协议的验证

Optimizing the MESI Cache Coherence Protocol for Multithreaded Applications on Small Symmetric Multiprocessor System

Cache is King -or- Things are about to get MESI

MESI Cache Coherency Protocol

其實想法很簡單, 如果是share part的部份.有write update 就 broadcast 出去,叫其他的 Cache update, 順便把data 寫回 memory, 如果是 read update 就只要 update 自己本身的 Cache 就好.

底下我們用sample emulator 來實現 MESI 的架構.

constrains:

CPU 的 schedule 為已知, 避免同時有兩個CPU 的 race condition.

cache 架構不是正式的 tags,block, valid. 只有考慮 address 跟 valid 的判斷.

有興趣的人可以抓來玩玩. ^_^

download here.

Refs:

Memory part 2: CPU caches

Cache工作原理-5

Cache Coherence

CMP中Cache一致性协议的验证

Optimizing the MESI Cache Coherence Protocol for Multithreaded Applications on Small Symmetric Multiprocessor System

Cache is King -or- Things are about to get MESI

MESI Cache Coherency Protocol

沒有留言:

張貼留言