在之前的 post 中提過 high level synthesis 的技術,如

ILP Scheduling with DVFS constrain @ perl,

Force-Directed Scheduling with golden check @ perl,

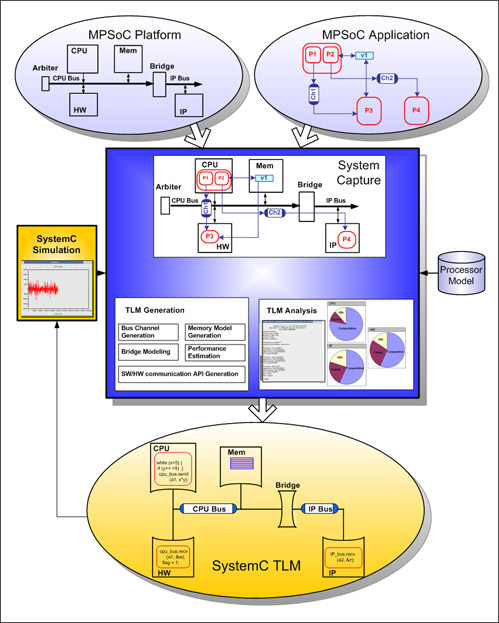

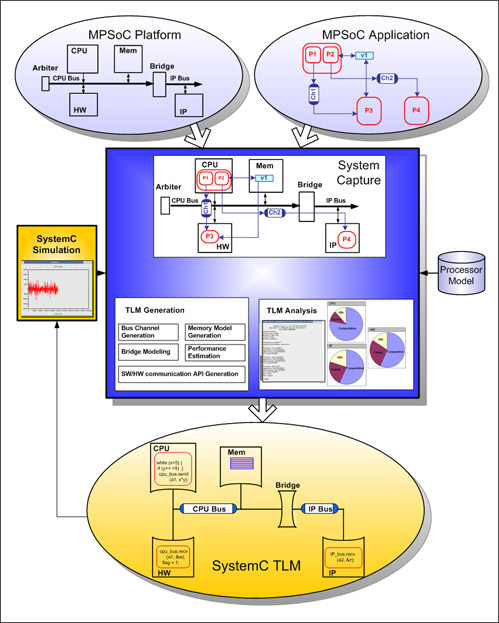

c to Verilog ..... 但這些技術其實跟compiler 多少都有關聯. 但以站在 Hardware Designer 的角度而言, 光從 fronted 到 backed 所要驗證的東西實在是太複雜了, 從 Algorithm define -> architecture map -> code gen -> function check -> time check -> RTL map -> FPGA -> layout -> chip test 這個 run time 少說也要個1-2年. 但以現在的 chip 規模而言, 傳統的是

IP Design 已經不能滿足 SOC 的 Platform. 所以在

ESE Technical Overview 中提及,如何透過 high level synthesis + platform constrain 的方式, 做 C to

FPGA direct map 的方式, 我們只要考慮好最上層的 algorithm 部份, 而中間的 schedule, assign, interface, hardware platform ...的部份就交給 tool set.藉此可解少我們在

IP design 時所花的時間,且達到 top - down 的 design flow. 其實說穿了就是利用

LLVM 的 virtual machine 做 front end 的 parser + schedule + merge + loop unrolling ... 而我們只要專心的把 back end 的 platform 建立起來就可達到快速的系統驗證.

ps: 不過這樣好像有一堆RD跟"我"一樣要失業了說...

XD

就 LLVM front end 而言,我們不需考慮到 compiler 是如何產生 AST(abstract syntax tree) 跟 node...的東西, 只要知道 LLVM 中間會產生一個 IR 的 file format. 而 IR 可以再轉成不同的平台的 machine code or language code. 且 LLVM 像 GCC 一樣有 plugins 的功能, 可以把自己寫好的 code complier 成 .so 檔. 之後再餵給 LLVM 當 extend lib. 看來又有很多 job 可以做了...

可以參考

LLVM Subsystem Documentation 內的

Writing an LLVM Backend Writing an LLVM Pass ...

Ref:

http://www.antlr.org/wiki/display/ANTLR3/LLVM

http://llvm.org/docs/ProgrammersManual.html#isa

basic block gen

http://llvm.org/releases/2.6/docs/tutorial/JITTutorial2.html

ESE

http://www.cecs.uci.edu/~ese/front-end.html

Build your own compiler in Ruby with LLVM

http://llvmruby.org/wordpress-llvmruby/

polygen grammar for LLVM assembly language.

Writing Your Own Toy Compiler Using Flex, Bison and LLVM

http://llvm.org/docs/ReleaseNotes.html#externalproj

在之前的 post 中提過 high level synthesis 的技術,如 ILP Scheduling with DVFS constrain @ perl,Force-Directed Scheduling with golden check @ perl, c to Verilog ..... 但這些技術其實跟compiler 多少都有關聯. 但以站在 Hardware Designer 的角度而言, 光從 fronted 到 backed 所要驗證的東西實在是太複雜了, 從 Algorithm define -> architecture map -> code gen -> function check -> time check -> RTL map -> FPGA -> layout -> chip test 這個 run time 少說也要個1-2年. 但以現在的 chip 規模而言, 傳統的是IP Design 已經不能滿足 SOC 的 Platform. 所以在ESE Technical Overview 中提及,如何透過 high level synthesis + platform constrain 的方式, 做 C to FPGA direct map 的方式, 我們只要考慮好最上層的 algorithm 部份, 而中間的 schedule, assign, interface, hardware platform ...的部份就交給 tool set.藉此可解少我們在 IP design 時所花的時間,且達到 top - down 的 design flow. 其實說穿了就是利用 LLVM 的 virtual machine 做 front end 的 parser + schedule + merge + loop unrolling ... 而我們只要專心的把 back end 的 platform 建立起來就可達到快速的系統驗證.

ps: 不過這樣好像有一堆RD跟"我"一樣要失業了說...XD

在之前的 post 中提過 high level synthesis 的技術,如 ILP Scheduling with DVFS constrain @ perl,Force-Directed Scheduling with golden check @ perl, c to Verilog ..... 但這些技術其實跟compiler 多少都有關聯. 但以站在 Hardware Designer 的角度而言, 光從 fronted 到 backed 所要驗證的東西實在是太複雜了, 從 Algorithm define -> architecture map -> code gen -> function check -> time check -> RTL map -> FPGA -> layout -> chip test 這個 run time 少說也要個1-2年. 但以現在的 chip 規模而言, 傳統的是IP Design 已經不能滿足 SOC 的 Platform. 所以在ESE Technical Overview 中提及,如何透過 high level synthesis + platform constrain 的方式, 做 C to FPGA direct map 的方式, 我們只要考慮好最上層的 algorithm 部份, 而中間的 schedule, assign, interface, hardware platform ...的部份就交給 tool set.藉此可解少我們在 IP design 時所花的時間,且達到 top - down 的 design flow. 其實說穿了就是利用 LLVM 的 virtual machine 做 front end 的 parser + schedule + merge + loop unrolling ... 而我們只要專心的把 back end 的 platform 建立起來就可達到快速的系統驗證.

ps: 不過這樣好像有一堆RD跟"我"一樣要失業了說...XD

就 LLVM front end 而言,我們不需考慮到 compiler 是如何產生 AST(abstract syntax tree) 跟 node...的東西, 只要知道 LLVM 中間會產生一個 IR 的 file format. 而 IR 可以再轉成不同的平台的 machine code or language code. 且 LLVM 像 GCC 一樣有 plugins 的功能, 可以把自己寫好的 code complier 成 .so 檔. 之後再餵給 LLVM 當 extend lib. 看來又有很多 job 可以做了...

可以參考 LLVM Subsystem Documentation 內的 Writing an LLVM Backend Writing an LLVM Pass ...

Ref:

http://www.antlr.org/wiki/display/ANTLR3/LLVM

http://llvm.org/docs/ProgrammersManual.html#isa

basic block gen

http://llvm.org/releases/2.6/docs/tutorial/JITTutorial2.html

ESE

http://www.cecs.uci.edu/~ese/front-end.html

Build your own compiler in Ruby with LLVM

http://llvmruby.org/wordpress-llvmruby/

polygen grammar for LLVM assembly language.

Writing Your Own Toy Compiler Using Flex, Bison and LLVM

http://llvm.org/docs/ReleaseNotes.html#externalproj

就 LLVM front end 而言,我們不需考慮到 compiler 是如何產生 AST(abstract syntax tree) 跟 node...的東西, 只要知道 LLVM 中間會產生一個 IR 的 file format. 而 IR 可以再轉成不同的平台的 machine code or language code. 且 LLVM 像 GCC 一樣有 plugins 的功能, 可以把自己寫好的 code complier 成 .so 檔. 之後再餵給 LLVM 當 extend lib. 看來又有很多 job 可以做了...

可以參考 LLVM Subsystem Documentation 內的 Writing an LLVM Backend Writing an LLVM Pass ...

Ref:

http://www.antlr.org/wiki/display/ANTLR3/LLVM

http://llvm.org/docs/ProgrammersManual.html#isa

basic block gen

http://llvm.org/releases/2.6/docs/tutorial/JITTutorial2.html

ESE

http://www.cecs.uci.edu/~ese/front-end.html

Build your own compiler in Ruby with LLVM

http://llvmruby.org/wordpress-llvmruby/

polygen grammar for LLVM assembly language.

Writing Your Own Toy Compiler Using Flex, Bison and LLVM

http://llvm.org/docs/ReleaseNotes.html#externalproj

沒有留言:

張貼留言