# \* breif sort + inverse

# * retrun [] */

def new_sort_0(i):

new_sort_0 = []

new_sort_1 = []

for j in range(i):

new_sort_0.insert(j,pow(2,j))

new_sort_0.insert(i,pow(2,i))

new_sort_1 = new_sort_0[:]

new_sort_1.reverse()

new_sort_1.pop(0)

return new_sort_0 + new_sort_1

# \* brief leaf 2 middle

# * return [] */

def new_sort_1(i):

new_sort = []

# @ leaf

for j in range(i):

new_sort.insert(j ,pow(2,j))

new_sort.insert(-(j+1),pow(2,j))

# @ middle

new_sort.insert(i,pow(2,i))

return new_sort

# @ run test

for i in range(5):

a = new_sort_1(i)

b = new_sort_0(i)

print a, b

del a, b

2011年7月29日 星期五

sad day ....

看來我的英文真是菜到爆,應該只有國小程度吧...XD,沒想到連考黑板題也寫的七七八八,真該撞牆好了.看來我還是沒有那個命阿.

題目:

> 5

print out 出底下 answer.

1

1 2 1

1 2 4 2 1

1 2 4 8 4 2 1

1 2 4 8 16 8 4 2 1

底下用 @ python

2011年7月28日 星期四

Samsung I9100 Galaxy S II new toy ....

最近買了人生中的第1支 "Smart Phone",很明顯的我是個不"smart"的人,居然跑去辦"韓國"人的機子,不過沒辦法誰叫人家真的是"強",雖然說明了就是"抄襲",但就是能做的出那種質感.HTC 是也不賴拉,但就市場定位來看,有愈來愈像 Nokia 的行銷手法.機海戰術要打到人心確實是有點難度,畢竟選擇太多很難讓人把焦點 focus 住,如果能像 "iphone" 一樣,把後端的 Service 做好一點.相信也還是有一定的水準的.

ps: S2 還滿方便的地方就是 synchronous 的功能,不像一般要透過條 usb 線,S2 只要用wifi 就可以跟 PC, TV 做 co-synchronous 的動作.

底下無聊,就整理些相關的 report,有興趣就看看吧

samsung_i9100_galaxy_s_ii spec

http://www.gsmarena.com/samsung_i9100_galaxy_s_ii-3621.php

root hack

http://forum.xda-developers.com/showthread.php?t=1125414

S2 games

http://www.galaxys2forums.com/samsung-galaxy-s2-games/

http://pdadb.net/index.php?m=search&quick=1

最近買了人生中的第1支 "Smart Phone",很明顯的我是個不"smart"的人,居然跑去辦"韓國"人的機子,不過沒辦法誰叫人家真的是"強",雖然說明了就是"抄襲",但就是能做的出那種質感.HTC 是也不賴拉,但就市場定位來看,有愈來愈像 Nokia 的行銷手法.機海戰術要打到人心確實是有點難度,畢竟選擇太多很難讓人把焦點 focus 住,如果能像 "iphone" 一樣,把後端的 Service 做好一點.相信也還是有一定的水準的.

ps: S2 還滿方便的地方就是 synchronous 的功能,不像一般要透過條 usb 線,S2 只要用wifi 就可以跟 PC, TV 做 co-synchronous 的動作.

底下無聊,就整理些相關的 report,有興趣就看看吧

samsung_i9100_galaxy_s_ii spec

http://www.gsmarena.com/samsung_i9100_galaxy_s_ii-3621.php

root hack

http://forum.xda-developers.com/showthread.php?t=1125414

S2 games

http://www.galaxys2forums.com/samsung-galaxy-s2-games/

http://pdadb.net/index.php?m=search&quick=1

2011年7月19日 星期二

MyHDL @ python

MyHDL 是個用 Python 的 HW simulator, 使用者可寫個類似像 Verilog 的 Python 語法, 之後在透過 Python 的 virtual machine 來做 simulation. 如果你夠懶, MyHDL 還提供 translator 的方式幫你把 Python 轉成 Verilog/VHDL.

ACTIVE_LOW, INACTIVE_HIGH = 0, 1

def Inc(count, enable, clock, reset, n):

""" Incrementer with enable.

count -- output

enable -- control input, increment when 1

clock -- clock input

reset -- asynchronous reset input

n -- counter max value

"""

@always(clock.posedge, reset.negedge)

def incLogic():

if reset == ACTIVE_LOW:

count.next = 0

else:

if enable:

count.next = (count + 1) % n

return incLogic

ps: 個人還是覺得用 SystemVerilog / SystemC 就 ok 了, 畢竟這還是主流. 至少有 EDA tool的廠商 support. 不過 Python 還真是好物, 可以用的 Lib 還真多, 不需要考慮物件的 type 跟 Memory release... 的問題. 多學點東西也是好的啦...XD

ref:http://www.myhdl.org/doc/current/

2011年7月15日 星期五

where is your Golden Model ?

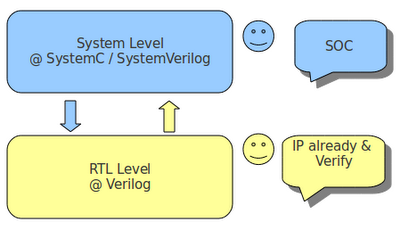

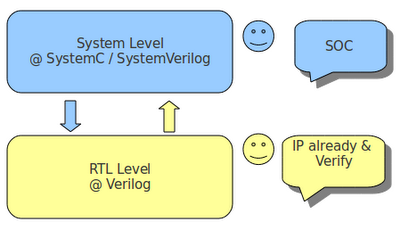

最近在推 ESL flow 中,發現很多公司的接受度不高,當然最主要的還是 ESL flow map 的問題,大致如下.

Questions:

1.公司現有的 RTL IP 都已經過驗證,為什麼還要 ESL flow?

2.Project 的時間性,沒有多餘的時間去驗證 ESL flow 是否符合現有的 Design flow?

3.ESL flow 的真實性,有沒有 FPGA 驗證?

4.ESL flow 可否 Synthesis 成 Gate Level 的 Design?

Answers:

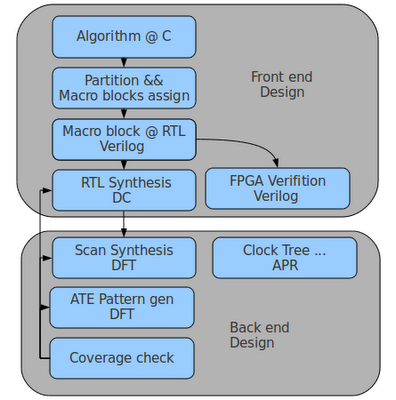

在現有的 Design flow,大致如下圖所示, 主要還是 RTL(verilog) -> Synthesis -> FPGA -> Software coding. 而這樣的 life time 會過長. 所以說 ESL 利用 top down 的 Design 方式,把 HW/SW co-design 到 virtual platform 上做 simulation 跟 verification. 可以較精確的評估出 system 的 performance 跟 bottleneck. 當然這是站在 ESL 的角度而言. 但如果今天能夠把現有的 RTL 轉成 ESL flow, 是不是又可以驗證出過去舊有的 Design 跟現有的 ESL 是否 match, 藉此找出彼此間的 gap, 可能是 time frame miss,system block 切不乾淨...的問題.等ESL 跟 RTL match 後, 是不是就可以把現有的 Design 跟新的 Design 做 co-synchronous, 達到 platform reusable 跟 system level 的最佳化.

ps: 當然現有 tool 都已 support "Soft IP". 而 Designer 可就現有的 Design 跟 Soft IP 結合的 virtual platform, 做初步的 simulation 跟 verification, 來決定哪個 platform or ip 是最符合公司的 requirement. 減少 try and run 的時間.

Questions:

1.公司現有的 RTL IP 都已經過驗證,為什麼還要 ESL flow?

2.Project 的時間性,沒有多餘的時間去驗證 ESL flow 是否符合現有的 Design flow?

3.ESL flow 的真實性,有沒有 FPGA 驗證?

4.ESL flow 可否 Synthesis 成 Gate Level 的 Design?

Answers:

在現有的 Design flow,大致如下圖所示, 主要還是 RTL(verilog) -> Synthesis -> FPGA -> Software coding. 而這樣的 life time 會過長. 所以說 ESL 利用 top down 的 Design 方式,把 HW/SW co-design 到 virtual platform 上做 simulation 跟 verification. 可以較精確的評估出 system 的 performance 跟 bottleneck. 當然這是站在 ESL 的角度而言. 但如果今天能夠把現有的 RTL 轉成 ESL flow, 是不是又可以驗證出過去舊有的 Design 跟現有的 ESL 是否 match, 藉此找出彼此間的 gap, 可能是 time frame miss,system block 切不乾淨...的問題.等ESL 跟 RTL match 後, 是不是就可以把現有的 Design 跟新的 Design 做 co-synchronous, 達到 platform reusable 跟 system level 的最佳化.

ps: 當然現有 tool 都已 support "Soft IP". 而 Designer 可就現有的 Design 跟 Soft IP 結合的 virtual platform, 做初步的 simulation 跟 verification, 來決定哪個 platform or ip 是最符合公司的 requirement. 減少 try and run 的時間.

Questions:

1.公司現有的 RTL IP 都已經過驗證,為什麼還要 ESL flow?

2.Project 的時間性,沒有多餘的時間去驗證 ESL flow 是否符合現有的 Design flow?

3.ESL flow 的真實性,有沒有 FPGA 驗證?

4.ESL flow 可否 Synthesis 成 Gate Level 的 Design?

Answers:

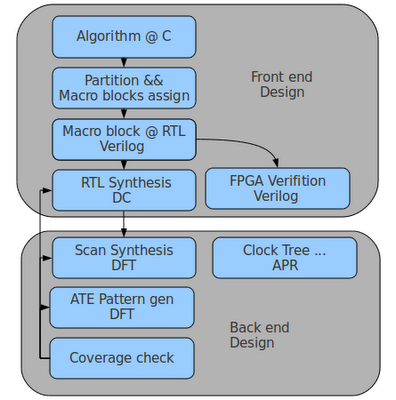

在現有的 Design flow,大致如下圖所示, 主要還是 RTL(verilog) -> Synthesis -> FPGA -> Software coding. 而這樣的 life time 會過長. 所以說 ESL 利用 top down 的 Design 方式,把 HW/SW co-design 到 virtual platform 上做 simulation 跟 verification. 可以較精確的評估出 system 的 performance 跟 bottleneck. 當然這是站在 ESL 的角度而言. 但如果今天能夠把現有的 RTL 轉成 ESL flow, 是不是又可以驗證出過去舊有的 Design 跟現有的 ESL 是否 match, 藉此找出彼此間的 gap, 可能是 time frame miss,system block 切不乾淨...的問題.等ESL 跟 RTL match 後, 是不是就可以把現有的 Design 跟新的 Design 做 co-synchronous, 達到 platform reusable 跟 system level 的最佳化.

ps: 當然現有 tool 都已 support "Soft IP". 而 Designer 可就現有的 Design 跟 Soft IP 結合的 virtual platform, 做初步的 simulation 跟 verification, 來決定哪個 platform or ip 是最符合公司的 requirement. 減少 try and run 的時間.

Questions:

1.公司現有的 RTL IP 都已經過驗證,為什麼還要 ESL flow?

2.Project 的時間性,沒有多餘的時間去驗證 ESL flow 是否符合現有的 Design flow?

3.ESL flow 的真實性,有沒有 FPGA 驗證?

4.ESL flow 可否 Synthesis 成 Gate Level 的 Design?

Answers:

在現有的 Design flow,大致如下圖所示, 主要還是 RTL(verilog) -> Synthesis -> FPGA -> Software coding. 而這樣的 life time 會過長. 所以說 ESL 利用 top down 的 Design 方式,把 HW/SW co-design 到 virtual platform 上做 simulation 跟 verification. 可以較精確的評估出 system 的 performance 跟 bottleneck. 當然這是站在 ESL 的角度而言. 但如果今天能夠把現有的 RTL 轉成 ESL flow, 是不是又可以驗證出過去舊有的 Design 跟現有的 ESL 是否 match, 藉此找出彼此間的 gap, 可能是 time frame miss,system block 切不乾淨...的問題.等ESL 跟 RTL match 後, 是不是就可以把現有的 Design 跟新的 Design 做 co-synchronous, 達到 platform reusable 跟 system level 的最佳化.

ps: 當然現有 tool 都已 support "Soft IP". 而 Designer 可就現有的 Design 跟 Soft IP 結合的 virtual platform, 做初步的 simulation 跟 verification, 來決定哪個 platform or ip 是最符合公司的 requirement. 減少 try and run 的時間.

2011年7月12日 星期二

UVM

最近發現個好物, UVM/OVM. 可以幫助 Designer 做 high level 的 performance/power estimation.不像以前還要自己刻個 "function class" + "Parser" 把每個 SystemC/System-Verilog Block 自動的掛到 virtual platform 上, 做簡單的 performance/power 的 simulation, 現在想想真是蠢呆了.

UVM/OVM support System-Verilog 讓 Designer 有 object oriented 的概念. 可 Extend, reused ...etc, 且能做到 High level 的 verification 如 算出 FSM, code, functional, path coverage ...可大幅提高 verification/ build platform 的速度.

ps: Eclipse 還真強大,連這都有真是佩服....

Refs :

http://www.dvteclipse.com/documentation/sv/Getting_Started.html

http://www.doulos.com/knowhow/sysverilog/uvm/

Refs :

http://www.dvteclipse.com/documentation/sv/Getting_Started.html

http://www.doulos.com/knowhow/sysverilog/uvm/

Refs :

http://www.dvteclipse.com/documentation/sv/Getting_Started.html

http://www.doulos.com/knowhow/sysverilog/uvm/

Refs :

http://www.dvteclipse.com/documentation/sv/Getting_Started.html

http://www.doulos.com/knowhow/sysverilog/uvm/

2011年7月9日 星期六

how to define "test / verify"

最近被問到如何去定義你的 test or verify. 當下就只有想到打 test patterns 去算 Coverage. 感覺不是個 good answer. 應該像是 Design flow 一樣, 根據不同的 Level 有不同的測試流程. 如 在Abstract Level, 測試 command 是否正確, 判斷是否會 overflow, 接著在 Communication Level, 測試 Communication 是否會 lost, 等架構都決定好後, 最後再做 Synthesis from RTL 2 Gate, 測試 Gate Level, 判斷是否會 short, Vdd, Gnd...etc Pass. 當然這都必須建立起每個 Level 的 test platform, 而在 OVM/VVM/UVM 可建立起在 Sytem Level 的 university verify model for functional testing. 可減少在 Software Designer 跟 Hardware Designer 之間的 Gap, 不用等到 Hardware Designer 把架構決定後 Software Designer 才開始 work. 把 Phase merge 起來, 減少 re-Debug / re- Define 的時間.

Ref:

http://www.doulos.com/knowhow/sysverilog/VMM/

http://www.testbench.in/

http://www.accellera.org/activities/vip

Ref:

http://www.doulos.com/knowhow/sysverilog/VMM/

http://www.testbench.in/

http://www.accellera.org/activities/vip

Ref:

http://www.doulos.com/knowhow/sysverilog/VMM/

http://www.testbench.in/

http://www.accellera.org/activities/vip

Ref:

http://www.doulos.com/knowhow/sysverilog/VMM/

http://www.testbench.in/

http://www.accellera.org/activities/vip

2011年7月5日 星期二

IC design vs Verification

底下是 ppt Tech_Job 的文章,看完之後還真頗有感覺.

看來只有做過的人才懂 Verify 的重要,不然我們永遠都在 RD(黑暗) 底下工作.

如果沒有我們, 即使在好的 Design 沒有經過實體的驗證 Flow,永遠只是天馬行空的想法.不過在台灣做 Verify 的人確實比較不被重視,真是該檢討一下才對...

=============================================================

作者: Muscato (科技始終來自於惰性) 看板: Tech_Job

標題: Re: [請益] IC design vs verification

時間: Sun Jun 19 11:11:32 2011

我想提供個不同的觀點

我本身也在美國工作過六年

當一開始一畢業的的 Ultrasparc CPU Design Verification

做到後來 48 port/16Gbps Fibre Channel Director 的 ASIC Design

中間做過的產品也得過 EMC Product of the year award

就是因為同時做過 Design 和 Verification,我才覺得 Verification 的重要

以一顆大型chip 來說,除非你是當到 Architect 等級了

不然當 Designer 很簡單,把你負責的 Block 搞好就是了

能真正看到 Whole Chip Level 的人不多

每個人負責的多半是一本spec 裡的一部份

管你裡面怎麼胡搞蝦搞,反正到最後 input/output 和 spec 規範的一樣

沒人理你裡面是不是一團漿糊

DV 呢? 從剛開始菜鳥來看,Designer 看的 Block Level Spec 你也要會

多半也還要幫忙 wholechip level debug

spec 你要看的比 designer 還熟,還細

因為你的責任就是雞蛋裡挑骨頭,把所有可能的問題找出來

等有經驗後,你要負責 Verification Env 的建構

也許有人會想,反正 Verilog/SystemVerilog 寫寫不就好了

是沒錯

但為什麼有人就是可以寫出一個很容易擴充的環境

在 RTL Sim 也許還看不出來

等到 Post Silicon Verification 的時候

Testbus 能看到的就那幾根毛

如何簡單快速的把在 silicon 遇到的問題在 RTL Sim 裡複製出來跑模擬

這才是功力所在

光用 random pattern + constraint 就快速打到你要寫 directed test 才打到的bug

這能夠省下無數寶貴的時間

VMM/Coverage/Assertion,每一項都有學問在

我還看過有人只用 Assertion 就可以把一個複雜的 module 驗到沒有 bug

我待過的公司都對 dv 的人客客氣氣,從不會有 design 就高人一等的感覺

沒有這些 dv,產品搞不好根本不能賣

說到分紅,我待過的公司從來都沒有差別待遇

分紅多與少,看的是你的表現

和產品賺不賺錢也沒什麼差

產品不賺錢,常常是上頭豬腦袋,沒做好市場研究或不會賣,不是產品沒做好

身為一個工程師,把產品做好,你的責任就盡到了

要說到 Job security,一個好的 dv 的人比一個 designer 安全的多

說到找工作,DV 的工作也比 designer 好找的多

特別是 Senior DV Enginner/Lead

要找到一個夠格的 DV Lead 比一個 Designer Engineer 難的多

因為太難養成一個夠水準的驗証工程師了

再說到當老闆往上爬? 我們這些工程師都一樣啦,早點看開比較不會受傷

管你 dv 還是 design,能爬到上面的有多少是純工程背景

多半都是 Marketing/Sales/Production 的人

為什麼?

因為他們最接近市場,他們知道客人要什麼,他們也能言善道會交際

同時,他們看的懂成本和收支表

還有,我並不喜歡學校/團隊至上論

我朋友 Oregon State MS,待的也不是什麼大公司團隊

一樣拿到 Waitrop 現在公司的 Offer

工作幾年後,看的是你的人脈和你在工作上學到了多少

看的是你面試臨場表現態度與你現場吸收學習的能力

學校能幫你畢業第一次,但不能幫你一輩子

共勉之

※ 引述《waitrop (嘴砲無雙)》之銘言:

: 不太想回文的,因為可能會變成一偏引戰文,

: 不過感覺還是有義務回文,

: 尤其是有興趣在美國發展的人,

: 以工作內容和人數而言,

: verification像是螞蟻雄兵,

: 公司裡頭撿垃圾的丐幫,

: 以前公司的高層說法,

: 一個designer要配三個verification的人,十個software,

: 實際上前公司的部門人數比也才1:1, 甚至verification人更少,

: 當然那跟政治環境有關係,掌權的人有人事權,

: 即使到了我現在的公司,人數比也大概1:2,

: verification大概兩倍的人,不過有些designer會幫忙驗證抓Bug,

: 而且人力真的很吃緊,預計verification還會繼續找人,

: 政治上,verification永遠在designer後面,

: 分紅獎金等也是如此,不過verification也算是designer一部份,

: 大致上看到的權力分配是(數位設計而言)

: core designer>core verification>SOC=system/software>layout,

: 當頭(VP, CTO, CEO)的都是core designer,

: 老二都是verification,只有非常少數是verification當頭,

: 不管是designer or verification 最終的目標都是當architect,

: 只有到那程度才有辦法設計晶片,掌握大局,

: 不然充其量也都只是繞線連線打雜,

: 目前的美國業界設計方式是由architect以及大頭們設計spec,

: 東西切乾淨再把每個block assign給designer/engineer,

: architect也先做好modeling, 可以預測結果以及效能,

: 如果是買IP,modeling跟verification這兩塊會變成最重要,

: 目前看到美國公司的工作情況是大部份會把layout outsource,

: 可能是國外,可以是外包公司,

: 甚至TSMC, tool company 願意提供這方面的服務,

: SOC跟繞線連線的工作也漸漸outsource,

: verification, system當然也是outsource, 尤其人力這麼吃緊,

: 留下來的大部份是不能換的architect, core design, core/architect verify,

: 就業方面,

: verification的確好找工作很多,也好換工做,

: 如果你學校學歷不是最好,經歷title低一點,公司團隊名聲差,

: verification會是你的機會,

: 當年我畢業的時候找了designer, architect modeling, verification,

: software是傻傻的投Google之類的公司,

: 結果拿到verification的工作,

: 這次換工做也是找這些工作,

: 最後也是verification公司最好, package最好,

: 前公司扣除特殊情況(不要再跟我吵特例),

: 大部份的新人designer都是要全美前十名學校,

: 即使是有經驗的人除非很強或公司團隊有名,不然學歷也是要前十名,

: 這已經是非常寬鬆的條件,

: 我目前的公司即使是MIT, Stanford畢業生都不一定有面試機會,

: 蘋果跟股歌只會更挑,

: verification就不一樣,

: 只要你願意打雜做黑的,畢業生學歷不太好都有機會做,

: 未來發展方面,

: 就像我之前說得,現在已經是IP Design年代,

: 大部份的公司都是買IP回來兜,

: 再加上tool越來越發達,純design, layout會越來越少,

: 即使是verification, 如果是block level 打訊號驗證,也不太需要了,

: 至少要到architect level才會有留下來的機會,

: 很多問題都是架構上的錯誤造成的,根本跟block design, IP無關,

: ※ 引述《javatea (:))》之銘言:

: : 進業界也滿一年多了 目前工作屬Deisng/SoC相關

: : 因為可能會轉換跑道 所以想多了解design及verification的未來性

: : 從美國的各大IC公司最近的機會來看 verfication需求越來越大

: : 除了最近跟一些senior聊過還有這一年多來對於產業的了解

: : 對於verification的觀感也跟在當學生的時候完全不同

: : 其實大部分的學生會偏向Design

: : 也真的是因為Design這個名詞好聽一些 根本沒給verficiation領域考慮的機會

: : 低估或者根本不考慮verification在整個IC/SoC的地位越來越重要

: : Verification並非單純像是test monkey般

: : 而是需要對design(無論IP or chip-level) 有一定程度的了解

: : 才能完成整個流程 我目前不完全了解這領域就是了...

: : 但感覺verification領域蠻有發展...不知道我的認知是不是算正確

: : 另外也希望有大大分享台灣Deisgn/verification的情況實際是如何呢?

: : 非常感謝

訂閱:

意見 (Atom)